an I-Connect007 publication

The Future of Nickel in Nickel/Palladium/Gold Final Finishes — p.18

# Plus:

Hunter's Two Newest CID Recipients Discuss Certification — p.46

Effective Decoupling Radius — p.52

# SURFACE FINISHES

Looking Below the Surface

IPC Plating Sub-committee 4-14: Surface Finish Specifications

by George Milad, page 10

# PCB BUYERScompare nearly 1900 manufacturers now at *The* PCB List.

Quick Search

Advanced Search

The best way to find a PCB fabricator, anywhere.

# HIGH-SPEED PCB DESIGN TRAING

- One-on-one mentoring

- Develop your skills with confidence

- Ensure your next design performs reliably

# This Issue: SURFACE FINISHES

# **FEATURED CONTENT**

For years, hot air solder leveling was the predominant surface finish in the PCB industry. But now, there's a veritable alphabet soup of available surface finishes, and each has its own advantages and disadvantages. This month, we focus on the latest in PCB surface finishes, with articles from George Milad and Rick Nichols, as well as columns and articles from our regular contributors.

10 Looking Below

the Surface —

IPC Plating

Sub-committee

4-14: Surface

Finish Specifications

by George Milad

**18** The Future of Nickel in Nickel/Palladium/Gold Final Finishes by Rick Nichols

# RF/Microwave Materials & Resources

- ► IS680 materials offers a complete laminate materials solution for single- and double-sided printed circuit designs and is a cost-effective alternative to PTFE and other commercial microwave materials.

- ► I-Tera® MT RF materials are available in 0.010", 0.020" and 0.030" in 3.38, 3.45 and 3.56 Dk.

- ▶ I-Tera® MT materials are suitable for both high-speed digital and RF/ microwave designs. A full compliment of cores and prepregs allowing flexibility in design is available in core thicknesses from 0.002" to 0.018".

- ► TerraGreen® halogen-free, very low-loss, thermoset materials are available in a variety of laminate and prepreg offerings. This material is inexpensive to process – improving your company's bottom line, as well as the environment.

- The revolutionary Astra® MT ultra low-loss thermoset laminates are a replacement for PTFE. These materials have been used for hybrid applications with Isola's 185HR and 370HR products.

|                                                         | RF/MICROWAVE MATERIALS                   |                            |                 |                 |                 |  |

|---------------------------------------------------------|------------------------------------------|----------------------------|-----------------|-----------------|-----------------|--|

|                                                         | IS680                                    | I-Tera® MT RF              | I-Tera® MT      | TerraGreen®     | Astra® MT       |  |

| Tg                                                      | 200°C                                    | 200°C                      | 200°C           | 200°C           | 200°C           |  |

| Td                                                      | 360°C                                    | 360°C                      | 360°C           | 390°C           | 360°C           |  |

| Dk @ 10 GHz                                             | 2.80 - 3.45                              | 3.38, 3.45 & 3.56          | 3.45*           | 3.45*           | 3.00            |  |

| Df @ 10 GHz                                             | 0.0028 - 0.0036                          | 0.0028, 0.0031 &<br>0.0034 | 0.0031*         | 0.0030*         | 0.0017          |  |

| CTE Z-axis (50 to 260°C)                                | 2.90%                                    | 2.80%                      | 2.80%           | 2.90%           | 2.90%           |  |

| T-260 & T-288                                           | >60                                      | >60                        | >60             | >60             | >60             |  |

| Halogen free                                            | No                                       | No                         | No              | Yes             | No              |  |

| VLP-2 (2 micron Rz copper)                              | Available                                | Available                  | Available       | Standard        | Standard        |  |

| Stable Dk & Df over the temperature range               | -55°C to +125°C                          | -55°C to +125°C            | -55°C to +125°C | -55°C to +125°C | -40°C to +140°C |  |

| Optimized global constructions for Pb-free assembly     | Yes                                      | Yes                        | Yes             | Yes             | Yes             |  |

| Compatible with other Isola products for hybrid designs | For use in double-<br>sided applications | Yes                        | Yes             | Yes             | Yes             |  |

| Low PIM < -155 dBc                                      | Yes                                      | Yes                        | Yes             | Yes             | Yes             |  |

# \* Dk & Df are dependent on resin content NOTE: Dk/Df is at one resin %. Please refer to the Isola website for a complete list of Dk/Df values. The data, while believed to be accurate & based on analytical methods considered to be reliable, is for information purposes only. Any sales of these products will be governed by the terms & conditions of the agreement under which they are sold.

### **RF Conversion Service**

- Isola's Design Review Service can facilitate your conversion to Isola's RF/microwave products and get you to market faster with the newest, ultra-low-loss materials.

- As part of this new service, Isola's technical staff will provide turn-key calculations, testing, characterizations and material recommendations to assist PCB fabricators and OEMs in converting to Isola's RF-materials, which will help overcome the current material shortages of other vendors and accelerate time-to-market. The design review service will also address the perceived conversion issues when migrating from a currently used material to an Isola material.

http://www.isola-group.com/conversion-service

# **FREE! Impedance and Power-Handling Calculator**

- Isola's free Impedance and Power-Handling Calculator predicts the design attributes for microstrips and striplines based on the design's target impedance and dielectric properties of the company's RF, microwave and millimeter-wave laminate materials.

- This software tool provides a design or an equivalent dielectric constant to facilitate modeling for PCB designers to predict impedance and other design attributes. The software computes changes in the effective dielectric constant due to dispersion at higher frequencies. The software then computes the total insertion loss a measure of power lost through heat for power handling calculations, including the dielectric loss, conductor loss, and the loss due to the surface roughness. The main factors affecting the typical power-handling capability of a material are its thermal conductivity, the maximum operating temperature, and the total insertion loss.

https://isodesign.isola-group.com/phi-calculator

**NUMBER 4**

MAGAZINE thepcbdesignmagazine.com

THE OPTIMUM

**MAGAZINE**

**DEDICATED TO**

**PCB DESIGN**

an I-Connect007 publication

# CONTENTS

# 46 Hunter's Two Newest CID Recipients

**Discuss Certification** by Kelly Dack

**52** Effective **Decoupling** Radius by Kirk Fabbri

**ARTICLES**

# **COLUMNS**

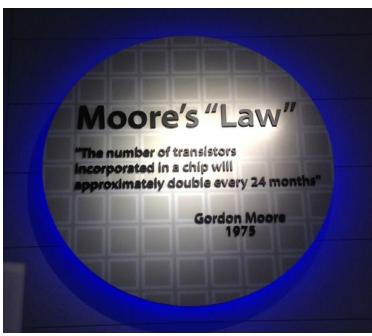

- 8 Moore's Law Turns 50 by Andy Shaughnessy

- **30** Learning the Curve by Barry Olney

- 36 RF Power Capabilities of **High-Frequency PCBs** by John Coonrod

**42** The Utility Belt by Tim Haaq

# VIDEO INTERVIEW

45 Altium Talks 3D Flex **Packaging Design**

### **SHORTS**

16 Removing Risk to Unleash the **Full Potential of Nanomaterials**

- 35 Breakthrough in Thermoelectric **Materials**

- **61** Driverless Cars to Renovate **Automotive Industry**

### **NEWS HIGHLIGHTS**

- 40 PCB007

- 50 Mil/Aero007

- 62 PCBDesign007

# **EXTRAS**

- **64** Events Calendar

- 65 Advertiser Index & Masthead

# The Absolute Best Value in High Technology Printed Circuit Boards

Since 1979, Eagle Electronics Inc. has provided our Customers with the highest quality Printed Circuit Boards at fair and competitive prices. We are committed to exceeding our Customers' expectations and requirements, acheiving total customer satisfaction on each and every job. It's just the way we do business!

With Eagle, you can expect:

- Rapid Response to Quote Requests

- Fair and Competitive Pricing/Costs

- 100% Quality Performance

- 100% On-Time Delivery Performance

- Flexibility Scheduling

- Stock/Consigned Inventory Programs

- Thorough follow-up after job completion

- Total Satisfaction!

click here for a virtual tour of our facility!

www.eagle-elec.com

# THE SHAUGHNESSY REPORT

# **Moore's Law Turns 50**

by Andy Shaughnessy I-CONNECT007

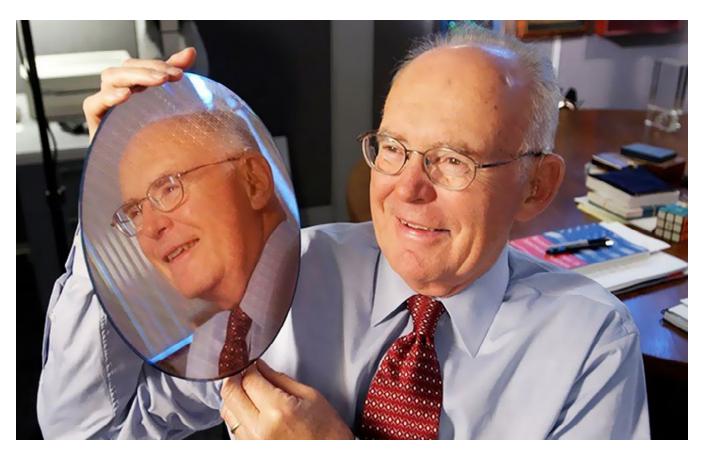

Let's all pause to wish Moore's Law a very happy 50th birthday, even as the vultures begin to circle overhead.

Fifty years ago, Dr. Moore was director of R&D at Fairchild Semiconductor, and Electronics Magazine asked him to make some predictions about the future of the semiconductor industry. On April 19, 1965, the magazine published his earthshaking article outlining what became known as Moore's Law.

In the article, titled "Cramming More Components onto Integrated Circuits," Moore posited that the number of components in a dense integrated circuit had doubled every year, and would continue at that rate for at least 10 years. Before he knew it, electronics companies around the globe were using Moore's Law for their technology roadmaps. It has become more than a target; it is one of the predominant driving forces in the electronics industry. In 1975, Moore amended his prediction from one year to approximately every two years. (Interestingly, Moore didn't come up with the term Moore's Law; that honor belongs to Caltech's Carver Mead.)

Moore went on to be a co-founder and CEO of Intel Corporation. He's had a great life; he and his wife created the Gordon and Betty Moore Foundation with a \$5 billion endowment. In 2001, the couple donated \$600 million to Caltech, the biggest single gift ever given to a college, and in 2007 they gave \$200 million to Caltech and the University of California to fund the Thirty Meter Telescope, to be built on Mauna Kae in Hawaii.

But all this time. Moore knew his law would hit a manufacturing wall. He once said, "It can't

# **MOORE'S LAW TURNS 50** continues

continue forever. The nature of exponentials is that you push them out and eventually disaster happens."

Now, as Moore's Law celebrates the big Five-O, technologists are predicting that the law will expire in the next decade. Chip companies are spending billions trying to identify the next material, or a new way to make chips.

# What's After Silicon?

A handful of new technologies show promise. Silicon nanophotonics involves replacing the electrons on an IC with light particles, and we know that light can transmit data through fiberoptic cables. Why not use light to move data on a chip? Talk about energy-efficient. Sure, nanophotonics are years away, but there's plenty of ongoing research in photonics.

IBM is investing in carbon nanotubes (CNT), and plans to have a CNT chip commercially available by 2020. CNTs have been around for over a decade. They exhibit amazing thermal conductivity, but creating them has been prohibitively expensive. Let's see how IBM brings down the price point on CNT technology.

IBM is also working with synaptic computing. Last year, the company revealed TrueNorth, the world's first neurosynaptic computer chip, which is designed to operate much like the human brain. TrueNorth features 5.4 billion tran-

sistors, the most that Big Blue has ever fit onto one chip. Sure, the human brain has 100 billion neurons, but that's a good first step.

But my favorite is quantum computing, which is still in the early experimental stages. Quantum computation encodes data into quantum bits (qubits), which can exist in "superpositions," or more than one state at once. This means that a qubit can represent a one and a zero at the same time, which is pretty cool.

All of these are in their infancy, and years from being commercially available. The big trick will be to create materials and processes that fit into the manufacturing flow of today, as seamlessly as possible. Good luck with that.

In the end, the electronics industry will have to make some adjustments when Moore's Law reaches the end of its life. But it won't be the end of the world that some of the chip companies imagine it to be. So, let's sing a round of "Happy Birthday" to Moore's Law and hold off calling hospice just yet. PCBDESIGN

Andy Shaughnessy is managing editor of *The PCB Design* Magazine. He has been covering PCB design for 15 years. He can be reached by clicking here.

# Surface Finish Specifications

# by George Milad

**UYEMURA** CO-CHAIR, IPC PLATING SUB-COMMITTEE 4-14

This article was previously published in the February 2015 edition of The PCB Magazine.

IPC specifications are reference documents to be called out by designers and OEMs. Designers may take exception with one or more items in the specification to ensure that the product meets the requirements of its intended use. The acronym AAUBUS (as agreed upon between user and supplier) is part of any specification.

Specifications are consensus documents. They are agreed upon by a panel of interested industry participants composed of suppliers, manufacturers, assembly houses (CMs) and end users. The IPC Plating Sub-committee 4-14 is no exception.

When there is consensus, the committee documents it in a specification. In cases where no consensus is readily arrived at, the committee undergoes its own testing in what is commonly referred to as a round-robin (RR) study. In a RR investigation, an agreed upon test vehicle (TV) is designed and manufactured. TVs are then sent around to the different suppliers who deposit the agreed upon thicknesses to be investigated. The TVs are collected and the deposit thicknesses are verified and documented. The TVs are then coded. The TVs are sent around again to the different testing sites that test for the desired attribute like soldering, contacting and wire bonding capabilities of different finish thicknesses. The data is then collected, sorted out and documented. At this point, a new attempt at consensus is made and upon arrival, the thickness specification is set.

A draft is prepared after consensus is complete. The draft is then posted for peer review. Any IPC member can review the document and suggest technical or editorial changes. All comments are then reviewed and all issues resolved

# INTRODUCING THE REVISION TRACKING HEADACHE AVOIDING FILE MANAGING KNOW WHO DID WHAT WHEN OCCAD EDM

# **Data Management Made Easy**

Let OrCAD° EDM handle your data management problems so you are free to focus on PCB design. OrCAD EDM puts revision control, check-in & check-out support, page management, and team configuration capabilities all inside the OrCAD Capture interface. This allows you to focus on creating new and differentiated products instead of trying to figure out which "version 7" of the latest design is actually the latest.

Learn how OrCAD EDM solves the PCB data management problem.

View Demo >

before the final draft is issued. At this time the IPC takes on the task of publishing the document in its final format.

The IPC Plating Sub-committee 4-14 has been active since 2001. It is co-chaired by myself and Gerard O'Brien of ST and S Group. The IPC liaison is Tom Newton. The sub-committee has an extensive member list composed of OEMs, contract assemblers, board manufacturers, chemical suppliers, as well as labs and consultants.

The committee operates through one-hour, bi-weekly conference calls. Calls are held every other Wednesday at 11:00 a.m., EST, and everyone is welcome to participate. A notification e-mail is sent out before each conference call. All decisions pertaining to initiation and follow up on round-robin studies, evaluation of results, draft review, etc., are made during these calls, by those in attendance. The call minutes are documented and circulated.

Since its inception, the IPC Plating Subcommittee 4-14 has issued the following:

- IPC-4552 ENIG Specification 2002

- IPC-4553 Immersion Silver specification 2005

- IPC-4554 Immersion Tin Specification 2007

- IPC-4553A Revised Immersion Silver 2009

- IPC-4554 Amended Tin Specification 2011

- IPC-4552 Amended ENIG Specification

- IPC-4556 ENEPIG Specification 2013

Following is a discussion of each of the above:

# **Electroless Nickel/Immersion Gold (ENIG)** IPC-4552, 2002

ENIG is a coplanar surface finish composed of a nickel layer capped with a thin layer of gold.

The ENIG surface finish is solderable, aluminum wire bondable, and an excellent contacting surface, with a minimum shelf life of 12 months under standard storage conditions. The immersion gold layer protects the underlying nickel from oxidation/passivation over its intended

criteria.

shelf life. Thickness specifications are set to ensure the ability of the finish to meet the above

> The ENIG IPC-4552 Specification was issued in 2002, and at the time of setting the specification for ENIG, no lead-free (LF) solder was in use. For thickness. IPC-4552 stated:

• The EN thickness shall be 3-6 µm [118.1 to 236.2 µin] The IG minimum thickness shall be 0.05 [1.97 µin], at four sigma (standard deviation) below the mean; typical values for IG of 0.075 to 0.125 um [2.955 to 4.925 µin]

Although no upper limit was set, the specification had a statement for suggested typical values for IG of 0.075 to 0.125 µm [2.955 to 4.925 µin]. These values were erroneously interpreted to be the specification.

The ENIG specification was amended in 2012:

- The lower limit for thickness was reduced from  $0.05 \mu m$  to  $0.04 \mu m$  ( $1.6 \mu in$ ) with the following restrictions:

- Limited time from manufacturing to assembly

- Demonstrate the consistency of the plating process

- Ability to measure low gold thickness

Presently, the ENIG 4552 is in revision and should be out in 2015 (Revision A). The objective of the revision is to set new lower and upper thickness limits for the immersion gold, to determine if the restrictions in the amended ENIG

surface, with a minimum

shelf life of 12 months

under standard storage

conditions.

# Quality PCBs from the established industry leader

With over 40 years of experience delivering high quality PCB prototypes, Sunstone Circuits® is committed to improving the prototyping process for the design engineer from quote to delivery.

We lead the industry with an on-time delivery rate of over 99%. Plus, our on-site technical support is available every day of the year (24/7/365), giving Sunstone unparalleled customer service.

Get a quote instantly at Sunstone.com

- Live customer support 24/7/365

- Over 99% on-time delivery

- Best overall quality & value in industry

- In business for over 40 years

- Online quote & order

- Free 25-point design review

- RF / exotic materials

- Flex / Rigid-Flex boards

- RoHS compliant finishes

- Free shipping & no NREs

- PCB123<sup>®</sup> design software

- Controlled impedance testing

spec could be lifted, to limit the typical pad size to be measured and to make the specification applicable to LF solder and LF conditioning. This entails an extensive RR study, presently in progress.

The intent is that the revised IPC-4552 Rev A would also include the following Additional Documents:

- Test method (TM) for stripping immersion gold during failure analysis

- Test method for determining the phos content of electroless nickel

- A corrosion chart setting acceptability criteria for nickel corrosion (black pad)

# **Immersion Silver (IAg)** IPC-4553 A, 2009

IAg is a thin, immersion silver deposit over copper. It is a multifunctional coplanar surface finish, applicable to soldering. It may also be applicable for some press-fit connections and as a contact surface. It has the potential to be suitable for aluminum wire bonding. The immersion silver protects the underlying copper from oxidation over its intended shelf life. Exposure to moisture and air contaminants, such as sulfur and chlorine, may negatively impact the useful life of the deposit. The impact can range from a slight discoloration of the deposit to the pads turning completely black.

Proper packaging is a requirement to achieve a 12-month shelf life.

# The Immersion Silver IPC-4553 Specification

In 2005, there were two distinct types of commercialized immersion silver with different thickness recommendations, referred to by the committee as "thin" and "thick." Each required its own thickness specification. This created much confusion as the terms were poorly defined.

The initial IPC-4553 Immersion Silver Specification specified two thicknesses and stated the following for thickness of deposit:

- Thin Silver: 0.05 μm(2μin) minimum at -2σ from process mean as measured on a pad of area  $2.25^{2} \mu m$  (3600<sup>2</sup> mils). Typical value 0.07  $\mu m$ (3µin) to 0.1 2µm (5µin)

- Thick Silver: 0.12 μm (5μin) minimum at -4σ from process mean as measured on a pad of area  $2.25^{2} \mu m$  (3600<sup>2</sup> mils). Typical value of 0.2  $\mu m$ (8uin) to 0.3 um (12uin).

In 2009, the immersion silver specification was revised. At this time the lower thickness supplier has discontinued his product and the industry was left with a common

> thickness from multiple suppliers. This revised specification only had one thickness specified (eliminating reference to thin and thick). The revised specification now includes an upper thickness limit. Typical values were recommended within the specified limits. The pad size for taking the thickness measurement was

also specified. The IPC-4553 Rev A Immersion Silver Specification stated the following for thickness of deposit:

• The immersion silver thickness shall be 0.12 µin [5 uin] minimum to 0.4 µm [16  $\mu$ in] maximum at  $\pm 4\sigma$  from process mean. Typical value between 0.2 µm [8 µin] to 0.3 µm [12 µin] as measured on a pad of area 2.25 mm<sup>2</sup> or 1.5 mm X 1.5 mm [approximately  $0.0036 \text{ in}^2 \text{ or } 0.060 \text{ in } X 0.060 \text{ in}] \text{ or equivalent.}$

# **Immersion Tin (ISn)** IPC-4554, 2007; amended 2012

The immersion tin (ISn) is a metallic finish deposited by a chemical displacement reaction that is applied directly to the basis metal of the printed board, which is copper. The immersion

tin is primarily used as a solderable surface for attachment of components. It may also be used when press-fit connections are employed and for zero insertion force (ZIF) edge connectors. The immersion tin finish protects the underlying copper from oxidation over the intended shelf life (storage of greater than six months) of this finish.

# **Immersion Tin IPC-4554 Specification**

For immersion tin, the committee specified a lower limit for thickness. The relatively thick value of 1 micron (40µin) was chosen to ensure that enough virgin tin would be available at the surface for soldering after extended storage. It is well understood that tin forms an intermetallic (IMC) layer with the underlying copper, and that this layer continues to grow in thickness over time.

The immersion tin thickness will be:

•  $\mu m$  (40  $\mu in$ ) minimum at -4 $\sigma$  from process mean as measured on a pad of area 2.252 µm (3600<sup>2</sup> mils) or equivalent. Typical value of 1.15 um ( (46 µin) to 1.3 µm (52µin).

The Immersion Tin Specification IPC-4554 was amended in 2011. The amendment addressed solderability testing and specified the allowed stress testing conditions for the deposit and the type of fluxes to be used for both tin/ lead and LF testing.

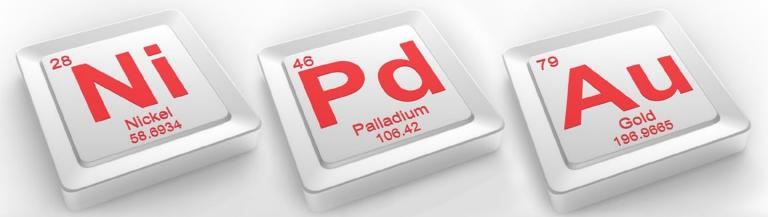

# **Electroless Nickel/Electroless Palladium/ Immersion Gold (ENEPIG)** IPC-4556, 2013

ENEPIG is a coplanar tertiary layered surface finish plated over copper as the basis metal. EN-EPIG consists of an electroless nickel base layer over which is plated an electroless palladium barrier layer followed by a deposit of a thin immersion gold as the final outer layer. It is a multifunctional surface finish, applicable to soldering and to gold, aluminum and copper wire bonding. It is also suitable as the mating surface for soft membrane and steel dome contacts. Additional applications include use in low insertion force (LIF) and zero insertion force (ZIF) edge connectors and for press-fit applications. The electroless palladium layer forms a diffusion bar-

rier that impedes nickel diffusion

to the gold surface. The immersion gold protects the palladium layer from reacting with contaminants prior to processing that might otherwise affect joining processes, such as wire bonding and soldering. ENEPIG has a minimum shelf life of 12 months under standard storage conditions. Thickness specifications are set to ensure the ability of the finish to meet all the attributed functionality.

tertiary layered surface finish plated over copper as the basis metal. ENEPIG consists of an electroless nickel base laver over which is plated an electroless palladium barrier layer followed by a deposit of a thin immersion gold as the final outer layer.

**ENEPIG** is a coplanar

# **Specification**

This is the last specification issued by the committee. The document produced is very comprehensive and includes a wealth of information from the RR studies that were conducted.

The ENEPIG IPC-4556

The Appendix contains a documentation of these studies, each authored by the principal who conducted the testing. It also includes a section on the proper methods of equipment setup for a reliable measurement of very thin layers of metal deposits.

The thickness specification for ENEPIG states:

- Nickel: 3 to 6 μm [118.1 to 236.2 μin] at ± 4 sigma (standard deviations) from the mean.

- Palladium: 0.05 to 0.15  $\mu$ m [2 to 12  $\mu$ in] at  $\pm$ 4 sigma (standard deviations) from the mean.

- Gold: minimum 0.025 µm [1.2 µin] at 4 sigma (standard deviations) below the mean. No upper limit was set for IG.

All measurements to be taken on a nominal pad size of 1.5 mm x 1.5 mm [0.060 in x 0.060 in] or equivalent area.

# **Organic Solderabilty Preservative (OSP)** IPC Specification (NONE)

OSPs are organic coatings that form a complex organo-metallic complex with the copper surface of the PWB. This complex preserves the solderability of the copper surface through assembly.

A wide variety of OSPs have evolved with the increasing complexity of the PWB. Initially, all that was required was a single thermal excursion for soldering leads into component holes, Then came surface mount that required at least two thermal excursions (one per side); add on top of that the need to hand solder an occasional rework. The biggest relevant evolution is lead-free assembly. LF assembly temperature at 260°C is approximately 35°C higher than eutectic soldering (225°C). The manufacturers of OSP have developed new OSPs to meet the market demands. These have a greater ability to withstand increasing number of thermal excursions and higher temperature, as needed for LE.

OSP products include benzotriazoles, imidazoles, benzimidiazoles and phenyl benzimidazoles. Some of the newer OSPs have additives occasionally referred to as "oxygen scavengers." These additives can stretch the performance window of the specific OSP. The more thermally robust coatings have significantly higher decomposition temperatures than the peak assembly reflow temperature. They require contact with appropriate flux and/or molten solder to penetrate the coating. They have longer shelf life, survive multiple reflow cycles and are more lead-free assembly compatible.

After more than one year of struggling with a specification for OSP, no consensus was reached, and no specification was set forth. This was due to the wide assortment of organic products that were used for solderability preservation for the various applications, each with its own thickness recommended values.

# Acknowledgement

To date, all committee activities have been voluntary and acknowledgement is in order for the members and equally important for their respective companies that allow for the time invested by their employees. PCBDESIGN

George Milad is the national accounts manager of technology at Uyemura International Corporation. He may be reached by clicking here.

# Removing Risk to Unleash the **Full Potential of Nanomaterials**

The EU-funded NANOREG project is developing the next generation of reliable and comparable experimental data on the environmental, health and safety aspects of nanomaterials. NANOREG, which began in March 2013, has already successfully established the basic conditions for its R&D work and will now move on to deliver on its key objectives.

Nanomaterials are chemical substances or materials that are manufactured at an incredibly small scale (down to 10 000 times smaller than the diameter of a human hair). Experts believe they have the potential to contribute significantly to Europe's

industrial competitiveness, and are already used in hundreds of products.

In order to fully capitalise on this potential market however, the safety of nanomaterials must be beyond reproach. As these nanomaterials are often unique and have never been on the market before, assessments must be done on a case-bycase basis using globally recognised and approved methods.

Regular meetings have also been set up with policy makers in partner countries, along with global standardisation institutions in countries like the

> US, Canada, Australia, Japan and Russia. The long term objective of NANOREG is to ensure that the innovative and economic potential of nanomaterials is not put at risk simply because health and safety issues have not been fully addressed.

# Pulsonix **Advanced Schematic** Capture and PCB Design Software

# A refreshing approach to simplifying Schematic Capture and PCB Design

- Import filters for all major tools (designs and libraries)

- Very easy to learn and use

- 5-Star Service and Support

**Download a Free Trial**

info@pulsonix.com www.pulsonix.com

# The Future of Nickel in Nickel/ Palladium/ **Gold Final Finishes**

# by Rick Nichols

ATOTECH DEUTSCHLAND GMBH

This article was previously published in the February 2015 edition of The PCB Magazine.

Final finishes can be subdivided into metallic and organic finishes. For the purpose of this article, the focus will be on the metallic finishes using the combinations of nickel (Ni) and/or palladium (Pd) and/or gold (Au). Variations on this theme are used extensively in the electronics market of today. The Ni/Pd/Au mutations are the inevitable result of technical requirement changes coupled with true and perceived acceptance within the industry. One such optimization is the phosphorus contents in the Ni and Pd layers. This subtlety will not be focused on in this article as the impact on the key topics is negligible.

This subgroup of metallic final finishes can also be further divided by their application bias. Traditional ENIG processes are biased towards using a protection layer to ensure extended lifetime reliability by protecting the base copper.

- Electroless nickel/immersion gold (ENIG) the workhorse

- Electroless nickel/electroless palladium (pure palladium and phosphor containing palladium)/immersion gold (ENEPIG) the all-purpose solution

The next-generation surface finishes need to be biased towards satisfying lifetime requirements in combination with enhanced technical performance.

• Electroless palladium/autocatalytic gold (EPAG)—fine-line, high-frequency, solder and bonding application

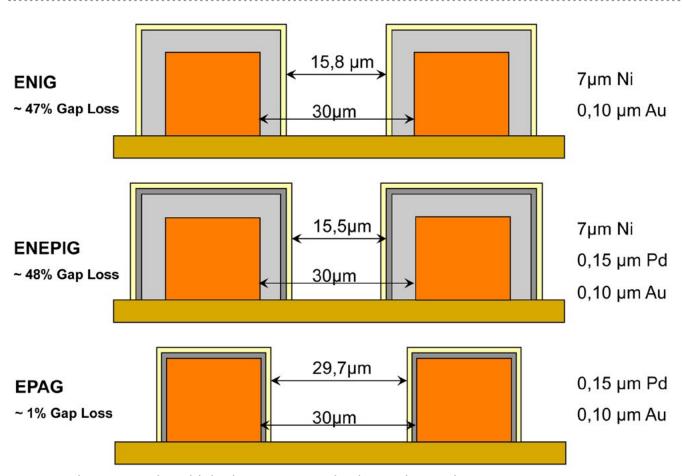

This broad segregation implies the inclusion or exclusion of Ni. This Ni protection layer (4–7 um) has a physical impact on line and space capability whilst simultaneously having a negative impact on high-frequency applications.

The symbiotic relationship between technology influences and the resultant require-

# We Take the Time to do it Right

because you don't have the time to do it over.

High quality quick turn manufacturing, just another reason we are America's Board Shop

ments for the final finish is the driving force for this article. It is also the intention of this article to highlight the superiority of the direct palladium processes in achieving the expected requirements of the future.

# **Generic Technical Requirements**

Regardless of the surface finish, there exist perceived and accepted minimum requirements for total functionality. The established standards will inevitably be augmented and many technology sectors will adopt their own performance criteria and expectations as the future era of high-frequency and fine-line applications become more necessary. It is also apparent that the new requirements will also include more economic wire bonding materials.

Despite being vital, solderability satisfies only part of the surface finish requirements. The surface finish must also provide adequate protection of the underlying copper circuitry from the time of substrate fabrication until packaging and assembly (copper corrosion on fine-line technology has the potential to impact significantly on signal integrity). The surface finish should not add to solder joint reliability concerns by contributing to the formation of undesirable intermetallic compounds (IMCs) or adversely affecting their growth. In other words, the bondability must be ensured.

Whilst negating all responsibility for looking into the future, some trends can be predicted as a result of integration trends. Circuit features continue to shrink and maintaining

|                                                 | Process                                        | ENIG                  | ENEPIG                            | EPAG                   |                       |

|-------------------------------------------------|------------------------------------------------|-----------------------|-----------------------------------|------------------------|-----------------------|

|                                                 | Thickness                                      | Ni: 5μm<br>AU: 0.07μm | Ni: 5μm<br>Pd:0.1μm<br>Au: 0.06μm | Pd: 0.1μm<br>AU: 0.1μm |                       |

| Soldering                                       | Multiple Soldering (> 3x soldering steps)      | *                     | *                                 | *                      |                       |

|                                                 | Solder Spread<br>(Eutectic Solder)             | *                     | *                                 | *                      |                       |

|                                                 | Solder Spread<br>(Lead Free Solder)            | *                     | *                                 | *                      |                       |

|                                                 | Solder Joint Reliability<br>(Eutectic Solder)  | *                     | <b>A</b>                          | *                      |                       |

|                                                 | Solder Joint Reliability<br>(Lead Free Solder) | <b>A</b>              | *                                 | *                      |                       |

|                                                 | Al Wire                                        | *                     | *                                 | *                      |                       |

| Wire Bondng                                     | Au Wire                                        |                       | *                                 | *                      |                       |

|                                                 | Pure Cu Wire                                   |                       | 0                                 |                        |                       |

|                                                 | Cu-Pd Wire                                     | •                     | *                                 | *                      |                       |

|                                                 | Ag Wire                                        | _                     | *                                 | *                      | 끝                     |

| High Frequency capability<br>(Skin Effect)      | Media and Sensor<br>Technology                 | •                     | •                                 | *                      | Future Considerations |

| Fine Line and Pitch<br>Capability<br>(>30:30µm) | Portable Media and<br>Sensor Technology        | •                     | •                                 | *                      | derations             |

| Shelf Life                                      | Shelf Life Prior to<br>Assembly                | ≥ 12 Months           | ≥ 12 Months                       | ≥ 12 Months            |                       |

| Very Good 🖈                                     | Good                                           | Sufficient O          | Limited <b>V</b>                  | No •                   |                       |

Figure 1: The generic capabilities of Ni, Pd and Au final finishes. Note: Electroless palladium/immersion gold (EPIG) has not been included due to the process's copper corrosion and poor wire bonding attributes.

# Solutions to Ensure PCB Manufacturing Success!

# **CAM350**

Verify and Optimize PCB Designs for Successful Manufacturing.

# BluePrint-PCB

Create comprehensive documentation to drive PCB fabrication, assembly and inspection.

Verify Design and Manufacturing Rules Any Time During the PCB Design Cycle.

At DownStream Technologies we are committed to delivering comprehensive solutions and workflow process improvements for all your PCB post processing needs.

For more information please visit downstreamtech.com or call 800-535-3226.

signal integrity becomes even more challenging. This has a direct impact on assembly, and in response future surface finishes need to accommodate newer adaptations of thermocompression bonding as the established solder technologies are also at the edge of their capabilities.

# **Topics and Considerations for Future Final Finishes**

# **Fine-line Technology**

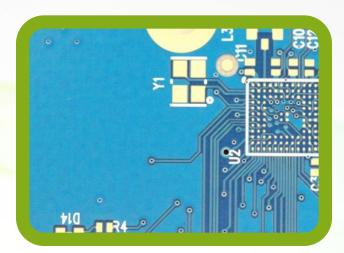

The concept of fine-line technology already has to factor in the impact of etching to arrive at the required line and space. For example, to achieve 10 µm line and space the circuit will be designed at 12 µm line and 9 µm space. After such painstaking front-end design, final finishes are faced with the challenge of maintaining this integrity as far as possible. With future fineline technology hinting at 5/5 and even 2/2 the final finish can no longer afford um scale protection layers such as Ni at 4-7 µm.

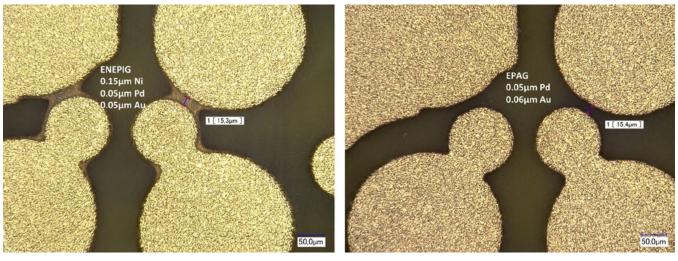

A further pitfall of the Ni inclusive technologies is their susceptibility to Ni spread and resultant shorting, even at an abnormally low Ni thickness (the low Ni is required to achieve the line and space criteria).

# **High-Frequency Capabilities**

The widespread use of smartphones and tablets to support daily employment and leisure activities is tangible evidence of the future appetite for high data flow capabilities which necessitates by virtue high-frequency capabilities. Based on history, it is clear that this insatiable appetite will continue to expand.

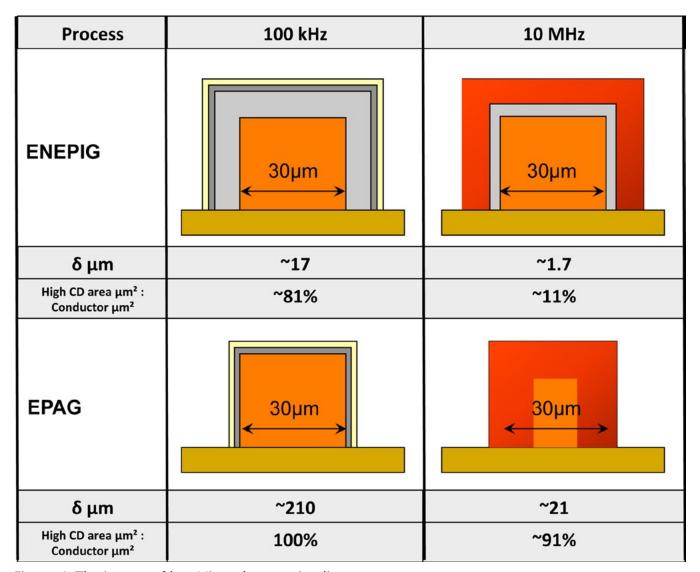

At very high frequencies surface finishes with a nickel layer become critical. It is known that nickel plated on copper will cause an ad-

Figure 2: The impact of established Ni containing finishes on line and space.

ditional loss to signal propagation due to the so called "skin effect." Initially proposed by Horace Lamb in 1883 for spherical conductors, it was then applied to conductors of any shape by Oliver Heaviside in 1885 (Wikipedia). In laymen's terms, the theory promulgates that induced electromagnetic fields (eddy currents) caused by alternating current will orientate the highest current density flow to the outside of the conductor. This is referred to as the skin effect. In turn, different conductor properties (electrical and magnetic) in conjunction with differ-

Figure 3: The potential for spreading when using a Ni inclusive finish.

Figure 4: The impact of frequency on skin depth ( $\delta$ ) with reference to process application.

ent frequencies will exhibit different skin depths ( $\delta$ ). With a given conductor property the skin-depth decreases exponentially with the increase of frequency.

The inclusion of Ni at 4–7 µm ensures that the primary signal will pass through the outer Ni skin. Not only is nickel a poorer conductor than copper, the effective area for the signal to pass through is greatly reduced. This is rather like placing your thumb over the end of a hose pipe, the resultant water flow is reduced and the directional flow is greatly disturbed.

The skin effect is one of the reasons why the electronics industry needs to entertain the notion of nickel-free surface finishes.

# **ENEPIG** 0.15μm Ni 0.05 µm Pd 0.05 µm Au EHT = 15.00 kV Signal A = AsB WD = 7.6 mm

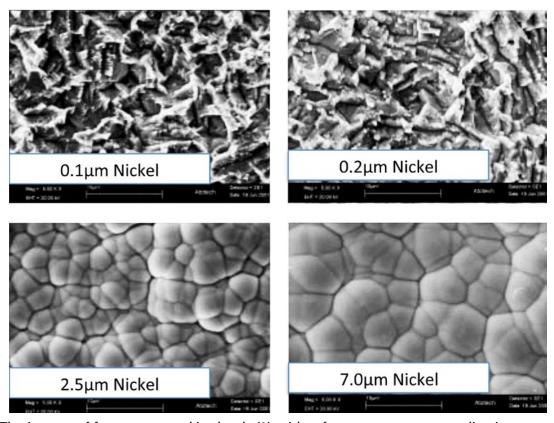

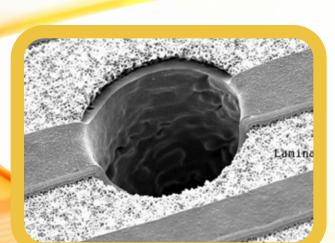

Figure 5: How the Ni morphology is influenced by the layer thickness.

# **ENIG**

Thousands of words have already been written about the workhorse, ENIG, and many panels have been processed successfully using it. This is an established process that fulfils the requirements of many existing and past applications but falls short of the requirements promised in the future. As such this process will not feature further in this article unless to make a comparison.

## **ENEPIG** with Thin Ni

Although in terms of words and production, the above is equally true for the "the allpurpose solution" (ENEPIG) process, this is the most promising of the Ni inclusive processes. In addition to performing well generically there a frequent question is raised within the industry:

# Why can't this process fulfil future requirements by employing a thin Ni layer?

Ni is employed as a barrier layer due to its dense crystal formations. The surface morphology, in turn is created by thicker Ni plating. This is the background for the IPC (4552 – ENIG and 4556 - ENEPIG), minimum thickness requirement of 3µm.

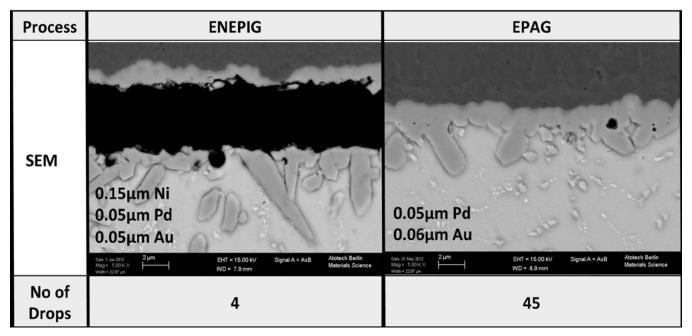

Higher Ni thicknesses positively influence the integrity of solder joints. By reducing the

Ni layer to conform to dimensions dictated by EPAG, dramatic quality issues are encountered. Early indications of this can be found by examining the intermetallic compound (IMC) by SEM. Whilst the IMC created using EPAG has no detrimental impact to the solder joint, the IMC created using EN (low thickness) EPIG displays evidence of demarcation lines.

Demarcation lines are cosmetically alarming and create concerns for the end-user. This is not an acceptable situation. The impact of demarcation lines, in terms of quality, can be demonstrated using a drop test. The drop test is a simulation of a handheld device being dropped.

According to the drop test, the performance of the EPAG system is superior to that of the thin Ni ENEPIG process. In addition to the poor drop test performance, the thin Ni layer becomes superfluous as a protection layer due to the low thickness and resultant poor morphology.

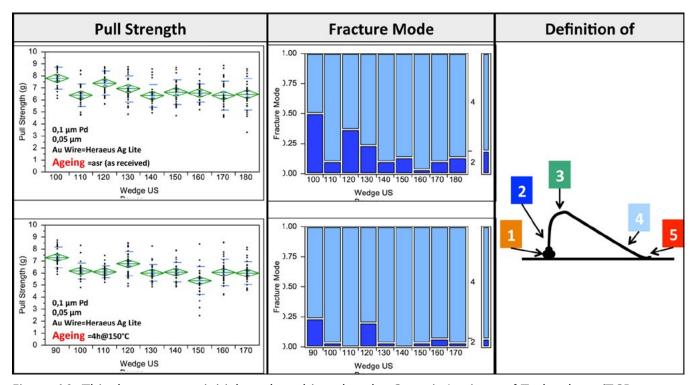

# Silver Wire Bonding

Wire bonding is a field that is evolving like any other. Bonding speed, wire hardness and cost are all in the mix. Some 3D packaging philosophies mean that wire bonding is here to stay unless it is replaced completely by flipchip derived bonding technology. Reduction in cost without yield and capacity loss is a ma-

Figure 6: The impact of low Ni on demarcation lines.

jor driver in this field. Pure copper wire bonding is one candidate for cost reduction, but this can result in other complications like component and equipment damage due to the forces and energy required. Gold, on the other hand, is the preferred and established medium, but recent exploration into silver wire bonding is proving potentially viable. The high potential for silver as a technical replacement for gold is the comparable softness of the metals. Figure 1 demonstrates that ENEPIG and EPAG are both able to deliver confidence in silver wire bondability. Additional to the technical similarities, silver also complies, in some way, to cost saving.

EPAG exhibits a wide working window with good performance indicators for silver wire bonding. Well known OEMs are also championing this direction for wire bonding. The results for Cu wire bonding are also acceptable.

# A Look into the Future

The roadmaps, available in the public domain, according to the following OEMs, IPC, iNEMI, ITRS and Jisso, predict fine-line technology. This, by definition, has a knock on impact to pitch miniaturization. This applies equally to organic and inorganic substrates.

As part of flip-chip bonding technology, the tried and tested reflow bonding is limited with

Figure 7: The performance comparison of the low Ni ENEPIG compared to the EPAG process.

Figure 8: Performance of EPAG for AG wire bonding.

regard to in/out (I/Os) density. With the value of real estate becoming so important, the space utilized by reflow bonding techniques is becoming an obstacle. When discussing real estate, it is common to solve the issue with an expansion in the Z-axis. In the property market this is fine, but in the portable electronics market this direction is also becoming crucial. The Z-axis constraints are high-speed signal transfer and

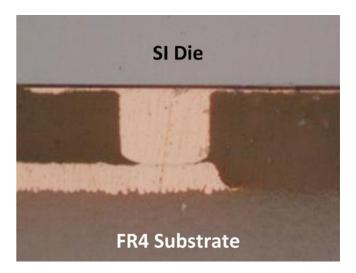

signal integrity. The reflow process requires the application of solder. Aside from this procedure being already at the application limit, the utilization of solder does not lie within the remit of controlled Z-axis expansion and is also a comparatively poor conductor compared to copper or other more noble metals. Here we have established that not only will the I/Os increase in density (decrease in pitch), but the pillar height (standoff height) will also become paramount to future developments. To this end Atotech is cooperating with Georgia Institute of Technology to assess the viability of using EPAG as the pillar and pad finish for thermo-compression bonding.

There exists a prior art to thermo-compression bonding (TCB). These can be characterized in Figure 9.

Although the prior art technologies are proven, there are some viable benefits in using EPAG as the copper interconnect. Not only can the key performance indicators or benefits can be compared to direct Cu-Cu bonding, but can be improved upon.

# **Conclusion**

Although ENIG and ENEPIG still have a place in a supplier's portfolio, the future is look-

" Providing Solutions to Board Fabrication Challenges"

# FROM CONCEPT TO COMPLETION

# **Solutions for Every Complex Situation**

At Multilayer Technology we have the skills and the knowledge to be able to say "Yes We Can!" to your most complex design requirements.

We specialize in High-Speed Digital and RF Design constraints. In addition, we offer the following solution-based services:

- Extensive Exotic Material Processing

- Pre-DFM Services Available

- State-of-the-Art Industry Leading Processes

- Space-Based Reliability Requirements Standard

**REQUEST A QUOTE**

3835 Conflans Rd Irving, TX 75061-3914

(972) 790-0062

|                                 |                           | Prior A                                                               | EPAG as Low T°C Cu                                    |                                                                  |  |

|---------------------------------|---------------------------|-----------------------------------------------------------------------|-------------------------------------------------------|------------------------------------------------------------------|--|

|                                 |                           | Current Direct Cu-Cu Bonding Curent Cu pillar with Solder-Cap Process |                                                       | interconnect                                                     |  |

| Pi                              | tch                       | Pure Cu interconnection <10μm                                         | Cu: Solder interconnect ~<br>25µm                     | Cu interconnect <10μm                                            |  |

| Properties                      | Electromigration          | > 1000 hours @10 <sup>-6</sup> A/cm²,<br>130°C                        | 10 <sup>-4</sup> - 10 <sup>-5</sup> A/cm <sup>2</sup> | > 1000 hours @10 <sup>-6</sup> A/cm², 130°C                      |  |

|                                 | Bonding T°C               | > 250°C                                                               | ~ 260°C                                               | < 200°C                                                          |  |

|                                 | Bonding t (s)             | 600                                                                   | <60                                                   | 30                                                               |  |

|                                 | Bonding Pressure          | High                                                                  | Low                                                   | High                                                             |  |

| Manufacturing<br>Considerations | Bonding<br>Environment    | Noble atmosphere or vacuum                                            | Air                                                   | Air                                                              |  |

|                                 | Non-Coplanarity<br>Offset | << 1μm (no bump collapse in solid-state bonding)                      | >3µm (high risk of bridging)                          | >3µm (bumping collapse under pressure, minor lateral deflection) |  |

Figure 9: The characteristics of prior art TCB compared to EPAG. (The highlights are in green.)

Figure 10: This demonstrates initial results achieved at the Georgia Institute of Technology (TCB at 190C – 3s – 365MPa with perfect electrical yield [1-2 $\Omega$ ]).

ing bright for the EPAG process. Hinged on the discussions above it is apparent that Ni presents some difficulties when considering its suitability within the scope of future requirements. The target of this article is to highlight the superiority of the EPAG process in ascertaining the goals of the future. PCBDESIGN

Rick Nichols is global product manager, selective finishing, at Atotech Deutschland GmbH. He may be reached by clicking here.

# TAKE A VIRTUAL TEST DRIVE AND THE VICTORY LAP IS YOURS

VALOR PCB MANUFACTURING SOFTWARE | Move into the fast lane with a free test drive of the latest manufacturing technology from Valor®. Get hands-on access to our lean NPI design verification, process preparation, and production planning tools from virtually anywhere. Complete your trial lap, and you'll be ready to cross the finish line with higher efficiency, performance, and productivity throughout your PCB manufacturing processes. Go ahead, take the wheel at www.mentor.com/drive

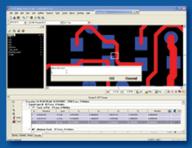

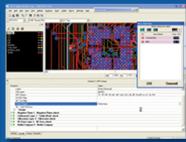

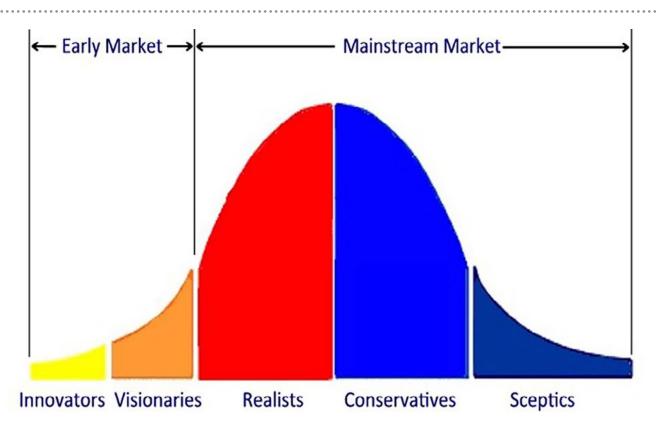

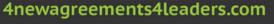

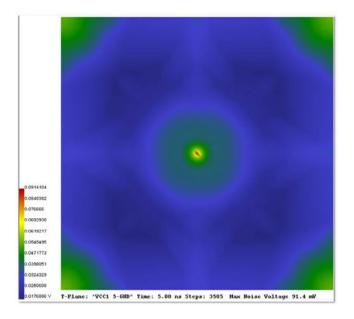

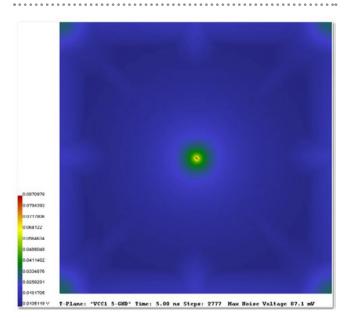

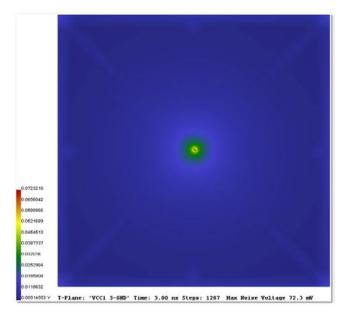

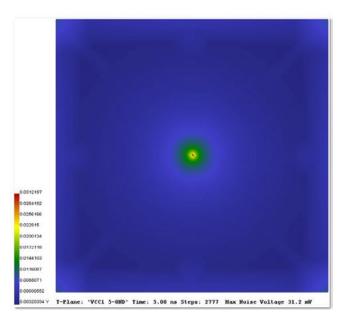

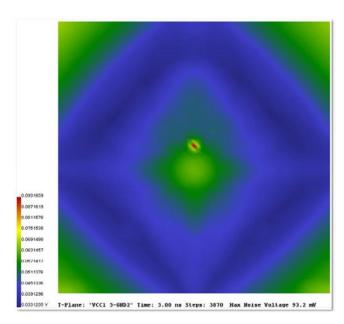

Currently, power integrity is just entering the mainstream market phase of the technology adoption life cycle. The early market is dominated by innovators and visionaries who will pay top dollar for new technology, allowing complex and expensive competitive tools to thrive. However, the mainstream market waits for the technology to be proven before jumping in. Power distribution network (PDN) planning was previously overlooked during the design process, but it is now becoming an essential part of PCB design. But what about the learning curve? The mainstream market demands outof-the-box, ready-to-use tools.

The mainstream market, representing more than 65% of the total EDA software market, wants established technology at an affordable

price. The majority of high-end tools require a PhD to drive. However, the mainstream market demands tools that are intuitive and can be used by any member of the development team from EEs to PCB designers to achieve quick results.

Inadequate power delivery can exhibit intermittent signal integrity issues. These include high crosstalk and excessive emission of electromagnetic radiation, degrading performance and reliability of the product. The PDN must accommodate variances of current transients with as little change in power supply voltages as possible. So the goal of PDN planning is to design a stable power source for all the required power supplies. As with stackup planning, the PDN design is required before a single IC is placed on the board.

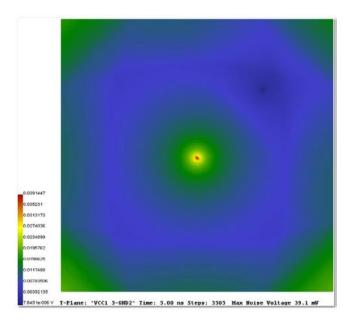

Figure 1: Technology adoption life cycle (Geoffrey A. Moore's Crossing the Chasm).

# How can you find the best PCB Partner? We can tell you. We wrote the book on it.

Choosing a PCB partner isn't hard—if you know what to look for. We've broken it down into "The 5 Commandments" and you can download it for free.

We are proud to be the Circuit Board Manufacturer of more than 400 growing companies, and even prouder to be a good partner for all our customers!

Click to Download

U.S. Circuit, Incorporated 2071 Wineridge Place Escondido, CA 92029 +1 (760) 489-1413 www.uscircuit.com

### **LEARNING THE CURVE** continues

Figure 2: PDN with optimized decoupling.

Also, the same PDN connections (planes) that are used to transport high-transient currents are used to carry the return currents for critical signal transmission lines. If high-frequency switching noise exists on the planes, coupling may occur, resulting in ground bounce, bit failure or timing errors. Many failures to pass electromagnetic compliancy (EMC) are due to excessive noise on the PDN coupling into external cables and radiating emissions.

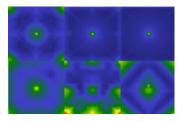

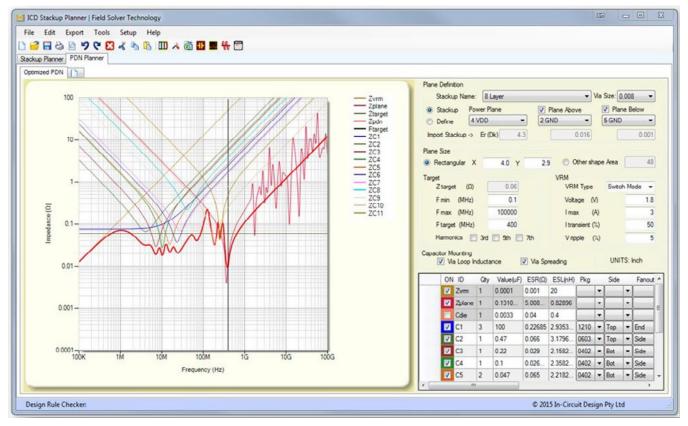

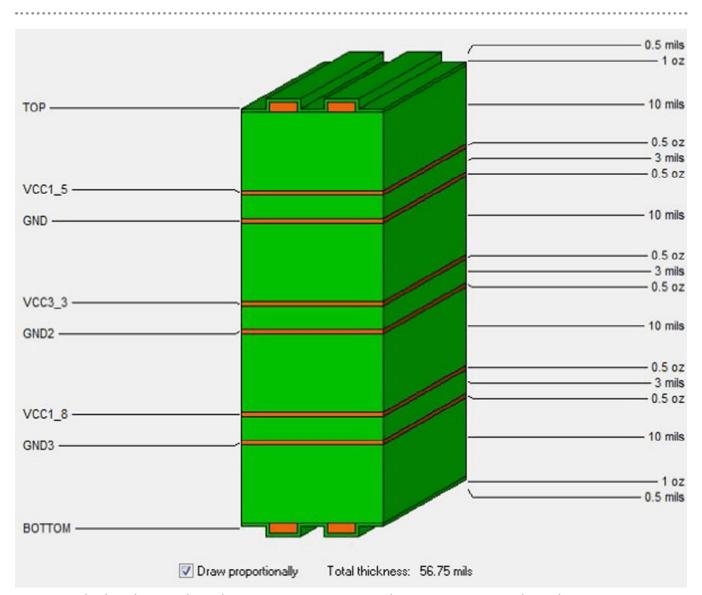

If you are not familiar with a PDN plot (AC impedance vs. frequency), it can be awfully daunting at first. Figure 2 shows the ICD PDN Planner with a typically 400MHz fundamental frequency and with an optimized capacitor selection. Please refer to my previous series PDN Planning and Capacitor Selection to understand the effects of bypass and decoupling capacitors on the PDN, as this column will focus on the plane resonance.

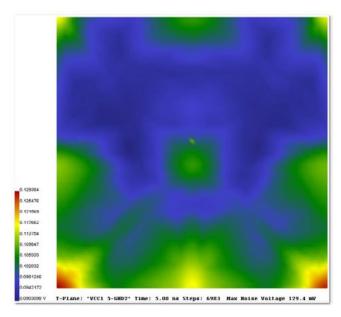

The AC impedance (thick red curve) should be below the target impedance up to the maximum bandwidth. For a 400MHz fundamental frequency, the maximum bandwidth is 2GHz to take in the 5<sup>th</sup> harmonic. But I am frequently asked one question: Does it have to be low all the way up to 2GHz?

In Figure 2, you will notice the ringing in the top right corner of the plot. This is the plane resonance. As the frequency approaches half wavelength, the planes (power and ground) act as an unterminated transmission line and start to resonate. This resonance is not a problem unless it falls on the fundamental frequency or one of the odd harmonics. A Fourier series expansion of a square wave is made up of a sum of odd harmonics. If the waveform has an even mark-to-space ratio then the even harmonics cancel.

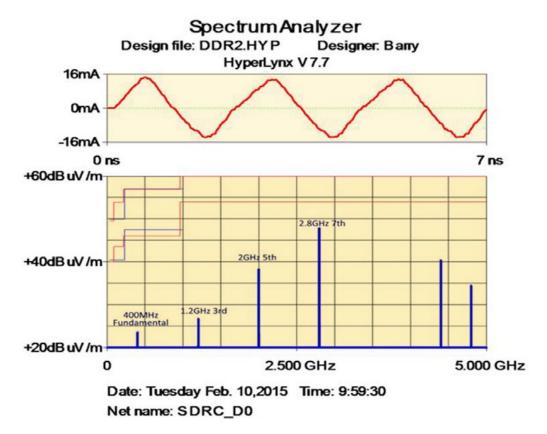

Figure 3 illustrates the typical electromagnetic (EM) radiation spectrum analyzer plot for a 400MHz DDR2 data signal. The fundamental frequency generally has little radiation, but then increases up to the 5th harmonic and re-

Figure 3: EM radiation from a DDR2 data signal @ 400MHz.

duces again with the higher harmonics. But I have seen cases where even the 11th harmonic— 4.4GHz in this instance—can create problems.

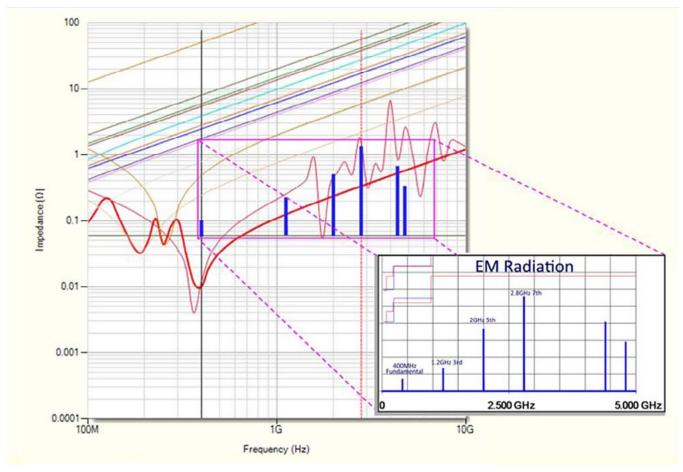

So what does this EM radiation have to do with the PDN analysis? If the AC impedance is high at the fundamental frequency or at any of the odd harmonics, then the board will radiate. In Figure 4, I have superimposed the EM radiation on the PDN plot. Look at where both the radiation and plane resonance peak. If these coincide, then you will have excessive radiation at that particular frequency. In this case, the fundamental 400MHz has a very low impedance so it will not be an issue. But, the 7th harmonic is high and the 5th is borderline. Fortunately, the amplitude diminishes as the frequency decreases.

I have pointed out a possible issue on the 5<sup>th</sup> and 7<sup>th</sup> harmonics in Figure 4, so how do we fix it? Decoupling capacitors are only effective below 1GHz, so no matter how many are added, to the PDN, they will not reduce the 2 and

2.8GHz peaks. However, above 1GHz, there are a number of ways to reduce the AC impedance:

- 1. On-die capacitance. Capacitors are placed on the IC itself by the manufacturer and generally cannot be changed. However, in some cases, the capacitors are on the top of the IC. It may be possible to piggyback parallel capacitors to increase their effect.

- 2. Reduce the loop inductance of the decoupling capacitors. This can be achieved by moving the decaps to the top side of the board so that the fanout vias have less distance to travel to the power and ground planes in the substrate. The loop inductance can also be reduced by using multiple vias per land and spacing them close to each other to reduce the loop area. But this reduced inductance has minimal effect above 1GHz.

- 3. Select a material with lower dielectric constant. This will push the plane resonance to a higher frequency.

# **LEARNING THE CURVE** continues

Figure 4: EM radiation overlapped on the PDN plane resonance.

- 4. Increase the planar capacitance. This is where the tight integration between the ICD Stackup Planner and PDN Planner comes into play. You can add, say, 3M embedded capacitance materials between the planes and then import this stackup back into the PDN Planner. This material typically has 20nF/in<sup>2</sup> capacitance and significantly reduces the AC impedance above 1GHz. Ultra-thin laminates are very expensive, but another option is to put two plane pairs, of twice the dielectric thickness, in parallel to achieve the same effect at a lower cost.

- 5. Modify the plane area (capacitance). Obviously, a DDR2 1.8V plane will not cover the entire area of the board. By reducing this area to as small as possible (2-square inches) the self-resonance of the plane will be moved up in frequency, reducing the AC impedance at the higher frequency and shifting the peaks. Reduc-

ing the plane area however, will also reduce the overall attenuation by increasing the characteristic impedance. Also, keep the area as square as possible. If you create a thin rectangular shape, then the plane resonances will increase due to the different standing wave ratios of the X and Y directions being uneven, thus creating more parallel resonance peaks.

The optimization of the PDN is a trial-anderror process that needs to be done in conjunction with the stackup materials to fully exploit all avenues. Suppressing the plane resonance peaks at the odd harmonics, to provide a low impedance profile at higher frequencies, also helps to minimize electromagnetic emissions.

### **Points to Remember**

• The mainstream market waits for the tech-

### **LEARNING THE CURVE** continues

nology to be proven before jumping in.

- This market, representing more than 65% of the total EDA software market, wants established technology at an affordable price.

- Inadequate power delivery can exhibit intermittent signal integrity issues.

- The PDN must accommodate variances of current transients with as little change in power supply voltages as possible.

- The AC impedance should be below the target impedance up to the maximum bandwidth (5<sup>th</sup> harmonic).

- As the frequency approaches half wavelength, the planes act as an unterminated transmission line and start to resonate. This resonance is not a problem unless it falls on the fundamental frequency or one of the odd harmonics.

- The fundamental frequency generally has little radiation but then increases up to the 5<sup>th</sup> harmonic and reduces again with the higher harmonics.

- If the AC impedance is high at the fundamental frequency or at any of the odd harmonics, the board will radiate.

Above 1GHz, there are a number of ways to reduce the AC impedance. The most effective being increasing planar capacitance and modifying the plane area. PCBDESIGN

### **References:**

- 1. Barry Olney's Beyond Design columns: PDN Planning and Capacitor Selection, Part 1 & Part 2; Power Distribution Network Planning

- 2. Geoffrey Moore: Crossing the Chasm For information on the ICD Stackup and PDN Planner, click here.

Barry Olney is managing director of In-Circuit Design Pty Ltd (ICD), Australia. The company developed the ICD Stackup Planner and ICD PDN Planner software, is a PCB Design

Service Bureau and specializes in board level simulation. To read past columns, or to contact Olney, click here.

# Breakthrough in Thermoelectric Materials

French physicist Jean Charles Athanase Peltier discovered a key concept necessary for thermoelectric (TE) temperature control in 1834. His findings were so significant that TE devices are now commonly referred to as Peltier devices. Since his work, there have been steady advancements in materials and design. Despite the technological sophistication Peltier devices, they are still less energy efficient than traditional compressor/evaporation cooling.

In the 1960s, Peltier devices were primarily

made from Bismuth-Telluride (Bi2Te3) or Antimony-Telluride (Sb2Te3) alloys and had a peak efficiency (zT) of 1.1, meaning the electricity going in was only slightly less than

the heat coming out. Since the 1960s there have been incremental advancements in alloy technology used in Peltier devices.

TE alloys are special because the metals have an incredibly high melting point. Instead of melting the metals to fuse them, they are combined through a process called sintering which uses heat and/or pressure to join the small, metallic granules.

The applications for such a material are abundant. As new fabrication techniques are developed, Peltier cooling devices may be used in place of traditional compression refrigeration systems. More importantly, as electrical vehicles and personal electronic devices become more ubiquitous in our daily lives, it is becoming increasingly necessary to have more efficient sys-

> tems for localized electrical power generation and effective cooling mechanisms. This new thermoelectric alloy paves the way for the future of modern TE devices.

# **LIGHTNING SPEED LAMINATES**

# RF Power Capabilities of High-Frequency PCBs

by John Coonrod ROGERS CORPORATION

I often hear this question: "How much RF power can be applied to a high-frequency PCB?"

My answer sometimes surprises engineers. I tell them that they can put as much RF power into the PCB as they want, with the assumption that the PCB does not exceed its maximum operating temperature (MOT). MOT refers to the maximum temperature to which a circuit can be exposed without degradation of critical properties. The actual RF power limit of a PCB is based on the MOT of the circuit, and that is dependent on the circuit material, the PCB construction and fabrication process.

The relative thermal index (RTI) is a rating given to UL-rated circuit materials for the maximum temperature to which the raw material can be exposed indefinitely without degradation in material properties. But when the raw material is made into a circuit, MOT is the rating that is most applicable to the power-handling capability of a circuit. The MOT is always less than a circuit material's RTI. When reviewing the maximum RF power-handling capabil-

ity of a PCB, MOT is used as the maximum temperature of which a circuit can be exposed over long periods of time.

For example, a circuit with a heat rise of +70°C above an ambient of +25°C must endure a temperature of +95°C indefinitely. The RF power which creates this heat rise is acceptable if the circuit has a MOT rating of +105°C. But if the circuit's heat rise is greater than +80°C above ambient, the applied RF power level that created the heat rise would not be acceptable.

When considering circuit heating due to applied RF power, modeling the heat rise of high-frequency PCBs can be difficult. Many variables influence heat rise, and they must be taken into account. Insertion loss is the total RF loss of a high-frequency PCB and is equal to the summation of conductor loss, dielectric loss, radiation loss and leakage loss. Insertion loss is the cause of the heat generated when RF power is applied. A circuit with a high level of insertion loss will generate more heat than a circuit with lower insertion loss, when considering the same

# DYMAX CONFORMAL COATINGS. BETTER PROTECTION AND HIGHER THROUGHPUT. BEYOND A SHADOW OF A DOUBT.

#### LIGHT-CURE CONFORMAL COATINGS

Dymax Conformal Coatings cure in seconds with UV light – and with ambient moisture curing available for shadowed areas, you can be confident you're getting maximum protection – even underneath components. Add vivid blue fluorescing for easy inspection of coating coverage, and you'll see more throughput, in less time, using less floor space. All with unsurpassed protection against moisture, dust, chemicals, and temperature cycling. And, they're backed by the Dymax Edge... an integrated offering of oligomers, customized adhesives and coatings, cure and dispense equipment, and application expertise that enables Dymax to deliver the best solution to the customer. Visit **dymax.com/pcbcoating** to download the new *Guide to Light-Cure Conformal Coatings*.

One major consideration

for understanding RF

power capabilities of a

high-frequency PCB is

to understand the

impact of insertion loss.

Generally, a circuit

material and design will

be chosen to minimize

insertion loss, but there

are tradeoffs and other

issues to consider.

#### RF POWER CAPABILITIES OF HIGH-FREQUENCY PCBS continues

amount of applied RF power. Insertion loss can also be difficult to model, because there are subcomponents that make up insertion loss. Typically, the major contributors to insertion loss are dielectric loss and conductor loss.

Dielectric loss is related to the dissipation factor (Df) and the tangent delta  $(\tan \delta)$  of the material. A material with higher Df causes higher dielectric loss, which in turn can cause higher insertion loss and high temperature rise with applied RF power. Conductor loss is far more complicated than dielectric loss, with several components making up conductor loss. In general, a circuit using copper with a rough surface will have more conductor losses than a circuit using smooth copper. Additionally, there is a circuit thickness relationship, and a thinner circuit will be more prone to conductor loss variables than a thicker circuit. The thicker circuit is more dominated by dielectric loss.

One major consideration for understanding RF power capabilities of a high-frequency PCB is to understand the impact of insertion loss. Generally, a circuit material and design will be chosen to minimize insertion loss, but there are tradeoffs and other issues to consider.

All circuit materials exhibit a property known as thermal conductivity: the measure of the ability to pass heat energy through that material. An extremely good thermal conductor is copper, which has a thermal conductivity value of 400 W/m/K. However, most substrates used for high-frequency PCBs have thermal conductivity values that are considered a thermal insulator or a very poor thermal conductor. Most high-frequency circuit materials have thermal conductivity values in the range of 0.2-0.4 W/m/K. A value of 0.5 W/m/K or higher is considered good for thermal conductivity for a PCB dielectric material.

Now, let's consider at quick tradeoff. There are some extremely low-loss PTFE materials which can be designed so the circuit will have minimal insertion loss. This means the circuit will generate less heat when RF power is applied and a designer may assume that higher power levels could be applied. However, many PTFE materials have very low thermal conductivity and even though there is less heat generated,

> the heat cannot efficiently get out of the circuit, so the circuit may heat more than expected.

> > Another tradeoff to consider is the thickness of the circuit. As an example, a doublesided circuit, which is a simple microstrip circuit bonded to a heat sink, will stay cooler if the circuit is thin, as opposed to thick, when using the same materials and same applied RF power. The thinner circuit has a shorter heat flow path from where the heat is generated at the signal conductor, through the dielectric and to the ground plane below which is attached to the heat sink.

There are several additional tradeoffs to consider, but a quick summary would show that the optimum circuit would use a material with low dielectric loss and smooth copper, which gives low insertion loss and generates less heat. Additionally, the optimum material would have high thermal conductivity and would be relatively thin.

A few high-frequency materials meet these criteria. When working with RF and microwave designs, consulting your materials provider can save you time and money. These companies have plenty of information about thermal conductivity, insertion loss, heat flow, overall thermal management, and much more. PCBDESIGN

John Coonrod is a senior market development engineer for Rogers Corporation. To read past columns, or to reach Coonrod, click here.

# We deliver Advanced PCB Solutions!

### **Landless Via Technology**

We're the only manufacturer in the world to have perfected a liquid photo-imageable resist (PiP) in electrolytic form, used for all our production.

**CLICK TO LEARN MORE**

Our unique processes enable us to create and deliver Advanced PCB Solutions that meet the needs of the demanding market at competitive prices!

### Fine line PCB, 2 mil line /space

We have developed a unique set of processes based on electro-depositable liquid photoresist.

**CLICK TO LEARN MORE**

### **Impedance Tolerance <5%!**

With our panel plating process combined with continuous foil lamination, our impedance tolerances are second to none!

**CLICK TO LEARN MORE**

CANDOR INDUSTRIES, INC.

**ADVANCED PCB SOLUTIONS**

### **PCB007**

### **News Highlights**

#### **How 3D Printing will Impact PCB** Fabrication

In the near future, we will enter an era where electronic devices are printed, rather than assembled. They will be fabricated layer-by-layer as a single object, rather than assembled from separate mechanical, electrical, and optical parts. This article describes the implications that 3D printing will have on PCB manufacturing.

#### **Material Witness: Low-Flow Prepregs— Defining the Beast!**

The term "low flow" should make sense to both suppliers and users of the products. A low-flow prepreg flows sufficiently to wet out and adhere to bonding surfaces and to fill innerlayer copper details, but does not flow so much as to fill in cutout areas in a heat sink or run unevenly out of the interface between rigid and flexible elements of a rigid-flex PWB.

#### Raising a Unified Voice for an **Advanced Manufacturing Economy**

The electronics manufacturing industry is an important sector in the global economy, and John Hasselmann, VP of Government Relations at IPC, is an advocate for policies that will help our industry, as well as the prosperity and welfare of billions of people.

#### **Reliability and Harmonization of Global** Standards at Forefront of EIPC Efforts

At IPC APEX EXPO 2015, I-Connect007 Technical Editor Pete Starkey caught up with EIPC's Michael Weinhold and Alun Morgan, who were happy to discuss both recent and ongoing focuses for EIPC, namely, reliability. Also touched on was the importance of the alignment of global standardization processes, especially for Asia.

#### FlexTech Honors Flex Electronics Firms

FlexTech Alliance awarded Thin Film Electronics, Vitex Systems and Pacific Northwest National Laboratories (PNNL), and California Polytechnic Institute's Graphic Communication Department with the 7th annual FLEXI Awards for Innovation, R&D, and Leadership in Education awards, respectively.

#### Schmoll Keeping an Eye on the Future and on LDI

In this interview, Thomas Kunz, who has been at the helm of Schmoll Maschinen as president since 1993, discusses the company's lengthy history in mechanical engineering (more than 70 years!), current global scope, and what he sees as a steady progression in directions that make the most sense to customers, which include laser direct imaging.

#### **IPC Volunteers Recognized at APEX**

IPC presented Committee Leadership, Distinguished Committee Service and Special Recognition awards at IPC APEX EXPO® at the San Diego Convention Center in February. The awards were presented to individuals who made significant contributions to IPC and the industry by lending their time and expertise through IPC committee service.

#### **IPC Opens Latest Statistical Programs**

IPC's global statistical programs for the laminate, solder, process consumables and assembly equipment industries are now open to new participants for 2015. The deadline for IPC members to sign up is April 15. Participation is free to IPC-member companies as a benefit of membership.

#### **Shennan Circuit Gets Top Supplier Award**

"Having a network of strong-performing suppliers that share our commitment to delivering exceptional quality and cost-effective solutions is essential to meeting our customers' needs," said Wayne Flory, vice president, material & supply for Rockwell Collins. "Shennan has been a strongperforming supplier since we started working with the company nearly ten years ago."

#### **HDI Leads Rigid PCB Growth in 2014**

High-density interconnect was still a main engine of growth in rigid PCB field in 2014, and is expected to maintain the momentum in 2015. As mobile phone screens become larger, PCBs for mobile phones have to react accordingly. To ensure light weight and thinness of mobile phones, the demand for more advanced anylayer HDI increases tremendously.

### INTRODUCING COOLSPAN® TECA

thermally & electrically conductive adhesive

#### Rogers can help by being your reliable conductive adhesive film source

Get the heat out of those high-power PCBs. COOLSPAN® Thermally & Electrically Conductive Adhesive (TECA) Films are ideal for dissipating heat in high-frequency circuits. COOLSPAN adhesives feature outstanding thermal conductivity (6 W/m/K) and reliable thermal stability. Keep things cool, with Rogers and COOLSPAN TECA film.

> **CONTACT YOUR SUPPORT TEAM TODAY**

www.rogerscorp.com

### MEET YOUR COOLSPAN® **TECA FILM SUPPORT TEAM**

Leading the way in...

• Support • Service • Knowledge • Reputation

#### SCAN THE CODE TO GET OUR CONTACT INFO.

Dale Doyle Western Territory

John Dobrick

Scott Kennedy

John Hendricks

**Kent Yeung** Regional

Sales Director

If you are unable to scan a VR code please visit our Support Team website at www.rogerscorp.com/coolspan

#### TIM'S TAKEAWAYS

# **The Utility Belt**

by Tim Haag INTERCEPT TECHNOLOGY

Back in school, I had planned on a career in music, specifically playing jazz clarinet or saxophone. But that didn't happen. Instead, I enjoyed a long career as a circuit board designer that eventually lead to my current career as a customer support and training manager.

Even though a career in music was never realized, many of the lessons learned during my musical training have helped me in this career. One of those lessons came from a grizzled old saxophone teacher who taught improvisational jazz. He drilled us on the basics of music: scales, chords, arpeggios, etc.

As he said, "You always want to have something in your pocket to pull from on those nights when you just aren't feeling as creative as usual." He was talking about having some basic jazz patterns to fall back on while improvising, but the same general concept can be applied in our industry: Make sure you have some good basic tools in your utility belt to help you out when you need them.

The utility belt is a great thing to have. Batman would be long dead without his, and Tim "The Tool Man" Taylor would be useless without his. But for a circuit board designer, a utility belt is equally important.

All of us at one time or another will have questions about the CAD system we use, and one essential tool to have in your utility belt is a list of people you can go to for help. At the top of this list should be your CAD system's friendly customer support staff (like me), so make sure that your company has current and up-to-date access to your CAD system's technical support.

I couldn't begin to tell you the many times that I have helped customers with a simple answer to a perplexing question. Just the other day I had a customer who was really stuck. He obviously knew our software well, but he was missing that one piece of information that he needed to break through the log-jam. I was able

# **Engineering And Providing Balanced Interconnect Solutions**

#### Flexible Printed Circuits • Rigid Flex • Wire Harnesses • Complete Assemblies

Our products and services are specifically designed to empower our customers to produce a product with superior performance and quality, as well as lower design, assembly, and system installation costs.